# **Product Specification Datasheet**

TNQ2LW6XL-CD104

### 100G QSFP28 LR4 Optical Transceiver

The QSFP28 LR4 is a 4x25G single-mode fiber, hot pluggable optical transceiver with unique technology enables the integration of 4 transmitters, 4 receivers and an optical MUX/ DeMUX into a small form factor package that delivers up to 112 Gbps data link in a compact QSFP28 footprint.

The optical connectivity is based on two Singlemode Fiber (SMF) LC connectors, one for Tx and one for Rx. The Tx and Rx each consist of 4 25GB/s LAN-WDM channels, whose wavelengths are in the 1300nm range. The QSFP28 LR4 transceiver is designed for applications with a reach up to 10Km.

#### **Features**

- Compliant with the QSFP28 MSA Technical Specifications.

- Supports operation for a data rate of 103.1Gb/s.

- Maximum link length of 10km on Single Mode Fiber (SMF).

- Optical specifications are compliant with IEEE802.3ba 100GBASE-LR4.

- Low speed electrical signal is compliant with SFF-8679.

- High speed electrical signal is compliant with 802.3bm CAUI-4.

- Digital diagnostic functions are available via the I2C interface, as specified by SFF-8636.

- 4x25Gb/s DFB-based LAN-WDM transmitter with central wavelengths of 4 channels 1295.56, 1300.05, 1304.58 and 1309.14 nm.

- Supports operation for a case temperature of 0°C to +70 °C.

- Duplex LC receptacles.

- Power Dissipation < 3.5W.

- Single 3.3V Power Supply.

- ROHS Compliant.

# **Applications**

• 100GBASE-LR4 Ethernet links

### **Absolute Maximum Ratings**

| Parameter                         | Symbol           | Min            | Max | Unit | Notes |

|-----------------------------------|------------------|----------------|-----|------|-------|

| Storage Temperature Range         | T <sub>STG</sub> | -40            | +85 | °C   |       |

| Supply Voltage                    | V <sub>cc</sub>  | 0              | 4   | V    |       |

| Maximum Average Input Optical     | P <sub>IN</sub>  | 5.5            |     | dBm  |       |

| Power per Lane (Damage Threshold) |                  |                |     |      |       |

| Relative Humidity                 | RH               | 10% to 90%     |     |      |       |

|                                   |                  | non-condensing |     |      |       |

## **Operating Conditions**

| Parameter                   | Symbol               | Min  | Max  | Unit | Notes |

|-----------------------------|----------------------|------|------|------|-------|

| Case Temperature- Operating | T <sub>CASE</sub>    | 0    | 70   | °C   |       |

| Supply Voltage              | Vcc                  | 3.14 | 3.46 | V    |       |

| Power Consumption           | P <sub>DISS</sub>    |      | 3.5  | W    |       |

| Power Consumption- LP Mode  | P <sub>DISS-LP</sub> |      | 1.5  | W    |       |

|                             |                      |      |      |      |       |

#### 100GBASE-LR4 Operation

| Transmitter Parameter                                    | Lane   | Min                               | Typical      | Max     | Unit  | Notes |

|----------------------------------------------------------|--------|-----------------------------------|--------------|---------|-------|-------|

| Signaling rate, each lane                                |        | 25.                               | 78125± 100 p | opm     | Gb/s  |       |

| Lane Wavelength Range                                    | Lane 0 | 1294.53                           | /            | 1296.59 | nm    |       |

|                                                          | Lane 1 | 1299.02                           | /            | 1301.09 | nm    |       |

|                                                          | Lane 2 | 1303.54                           | /            | 1305.63 | nm    |       |

|                                                          | Lane 3 | 1308.09                           | /            | 1310.19 | nm    |       |

| Average Optical Power per lane                           |        | -4.3                              |              | 4.5     | dBm   |       |

| Total Average Launch Power                               |        |                                   |              | 10.5    | dBm   |       |

| Optical Modulation Amplitude (OMA), each lane            |        | -1.3                              |              | 4.5     | dBm   |       |

| Launch Power in OMA minus TDP, each lane                 |        | -2.3                              |              |         | dBm   |       |

| Transmitter and Dispersion Penalty (TDP) each lane       |        |                                   |              | 2.2     | dB    |       |

| Average Launch Power per Lane @ TX Off State             |        |                                   |              | -30     | dBm   |       |

| Extinction Ratio                                         |        | 4                                 |              |         | dB    |       |

| Relative Intensity Noise (OMA)                           |        |                                   |              | -130    | dB/Hz |       |

| Side-Mode Suppression Ration (SMSR)                      |        | 30                                |              |         | dB    |       |

| Optical Return Loss Tolerance                            |        |                                   |              | 20      | dB    |       |

| Transmitter Reflectance                                  |        |                                   |              | -12     | dB    |       |

| Transmitter Eye Mask Definition {X1, X2, X3, Y1, Y2, Y3} | {0     | 0.25, 0.4, 0.45, 0.25, 0.28, 0.4} |              |         | 1     |       |

| Transmitter Output Power Monitor Accuracy                |        | -3                                |              | 3       | dB    |       |

| Receiver Parameter                                       | Lane   | Min                               | Typical      | Max     | Unit  | Notes |

| Signaling rate, each lane                                |        | 25.                               | 78125± 100 p | opm     | Gb/s  |       |

| Lane Wavelength Range                                    | Lane 0 | 1294.53                           | /            | 1296.59 | nm    |       |

|                                                          | Lane 1 | 1299.02                           | /            | 1301.09 | nm    |       |

|                                                          | Lane 2 | 1303.54                           | /            | 1305.63 | nm    |       |

|                                                          | Lane 3 | 1308.09                           | /            | 1310.19 | nm    |       |

| Damage Threshold                                         |        | 5.5                               |              |         | dBm   |       |

| Average Receive Power, each lane                         |        | -10.6                             |              | 4.5     | dBm   |       |

| Receive Power, each lane (OMA)                           |        |                                   |              | 4.5     | dBm   |       |

| Receiver Reflectance                                     |        |                                   |              | -26.0   | dB    |       |

| Receiver Sensitivity (OMA) per lane                      |        |                                   |              | -8.6    | dBm   | 2     |

| Stressed receiver sensitivity(OMA),each lane             |        |                                   |              | -6.8    | dBm   | 3     |

| Receive Power Monitor Accuracy                           |        | -3.0                              |              | 3.0     | dB    |       |

#### Notes:

- 1.Hit ratio 5x10<sup>-5</sup>

- 2.Measured with a test pattern of PRBS 2<sup>31</sup>-1 at Pre-fec BER 1x10<sup>-12</sup>

- 3. Measured with vertical eye closure penalty of 1.8 dB max, J2 of 0.30 UI, and J9 of 0.47 UI.

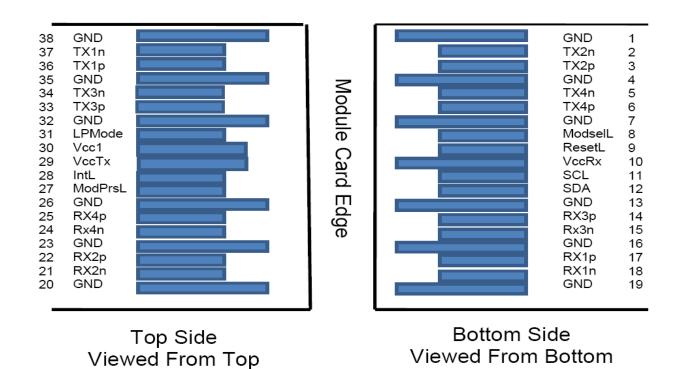

## **QSFP28 Connector and Pinout Description**

The electrical interface to the transceiver is a 38 pins edge connector. The 38 pins provide high speed data, low speed monitoring and control signals, I2C communication, power and ground connectivity. The top and bottom views of the connector are provided below, as well as a table outlining the contact numbering, symbol and full description.

Figure 1. QSFP28-compliant 38-pin connector

# **QSFP Transceiver Pinout**

| 1         GND         Ground         1           2         CML-I         TX2n         Transmitted Inverted Data Input         3           3         CML-I         TX2p         Transmitted Non-Inverted Data Input         3           4         GND         Ground         1           5         CML-I         TX4n         Transmitted Inverted Data Input         3           6         CML-I         TX4p         Transmitted Non-Inverted Data Input         3           7         GND         Ground         1         1           8         LVTTL-I         ModSeil         Module Select         3         9         LVTL-I         Resett         Module Reset         3         10         Vcc Rx         +3.3 VDC Receiver Power Supply         2         11         LVCMOS-I/O         SCL         Serial Clock for I2C Interface         3         3         12         LVCMOS-I/O         SDA         Serial Data for I2C Interface         3         12         LVCMOS-I/O         SDA         Serial Data for I2C Interface         3         12         LVCMOS-I/O         SDA         Serial Data for I2C Interface         3         12         LVCMOS-I/O         SDA         Serial Data for I2C Interface         3         12         CML-O         RX                                                                            | Pin No.  | Logic      | Symbol  | Description                         | Plug Sequence |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------|---------|-------------------------------------|---------------|

| 2 CML-I TX2p Transmitted Inverted Data Input 3 3 CML-I TX2p Transmitted Non-Inverted Data Input 3 4 GND Ground 1 5 CML-I TX4p Transmitted Inverted Data Input 3 6 CML-I TX4p Transmitted Inverted Data Input 3 7 GND Ground 1 8 LVTTL-I ModSeil Module Select 3 9 LVTTL-I ResetL Module Reset 3 10 VC RX +3.3 VDC Receiver Power Supply 2 11 LVCMOS-I/O SCL Serial Clock for I2C Interface 3 12 LVCMOS-I/O SDA Serial Data for I2C Interface 3 13 GND Ground 1 14 CML-O RX3p Receiver Non-Inverted Data Output 3 15 CML-O RX3p Receiver Inverted Data Output 3 16 GND Ground 1 17 CML-O RX1p Receiver Inverted Data Output 3 18 CML-O RX1n Receiver Inverted Data Output 3 19 GND Ground 1 20 GND Ground 1 21 CML-O RX2p Receiver Inverted Data Output 3 22 CML-O RX2n Receiver Inverted Data Output 3 23 GND Ground 1 24 CML-O RX2p Receiver Inverted Data Output 3 25 CML-O RX4p Receiver Inverted Data Output 3 26 GND Ground 1 27 LVTIL-O ModPrsL Module Present 3 28 LVTIL-O IntL Interrupt 3 29 Vcc TX +3.3 VDC Transmitter Power Supply 2 30 Vcc TX +3.3 VDC Transmitter Power Supply 2 31 LVTIL-I LPMode Low Power Mode 3 32 GND Ground 1 33 CML-I TX3p Transmitted Inverted Data Input 3 34 CML-I TX3p Transmitted Inverted Data Input 3 36 CML-I TX1p Transmitted Inverted Data Input 3 37 CML-I TX1n Transmitted Inverted Data Input 3        |          |            |         | ·                                   |               |

| 3 CML-I TX2p Transmitted Non-Inverted Data Input GND Ground 1 5 CML-I TX4n Transmitted Inverted Data Input 3 6 CML-I TX4p Transmitted Inverted Data Input 3 7 GND Ground 1 8 LVTTL-I ModSeil Module Select 3 9 LVTTL-I ResetL Module Reset 3 10 Vcc Rx +3.3 VDC Receiver Power Supply 2 11 LVCMOS-I/O SCL Serial Clock for I2C Interface 3 12 LVCMOS-I/O SDA Serial Data for I2C Interface 3 13 GND Ground 1 14 CML-O RX3p Receiver Non-Inverted Data Output 3 15 CML-O RX3n Receiver Inverted Data Output 3 16 GND Ground 1 17 CML-O RX1p Receiver Non-Inverted Data Output 3 18 CML-O RX1n Receiver Inverted Data Output 3 19 GND Ground 1 20 GND Ground 1 20 GND Ground 1 21 CML-O RX2n Receiver Inverted Data Output 3 22 CML-O RX2n Receiver Inverted Data Output 3 23 GND Ground 1 24 CML-O RX2p Receiver Inverted Data Output 3 25 CML-O RX4p Receiver Inverted Data Output 3 26 GND Ground 1 27 LVTTL-O ModPrsL Module Present 1 28 LVTTL-O Intl. Interrupt 3 29 Vcc Tx +3.3 VDC Transmitter Power Supply 2 30 Vcc Tx +3.3 VDC Power Supply 2 31 LVTTL-I LPMode Low Power Mode 3 32 GND Ground 1 33 CML-I TX3p Transmitted Inverted Data Input 3 34 CML-I TX3n Transmitted Inverted Data Input 3 36 CML-I TX1p Transmitted Inverted Data Input 3 37 CML-I TX1p Transmitted Inverted Data Input 3 37 CML-I TX1n Transmitted Inverted Data Input 3 | 2        | CMI-I      |         |                                     | 3             |

| 4 GND Ground 1 5 CML-I TX4n Transmitted Inverted Data Input 3 6 CML-I TX4p Transmitted Inverted Data Input 3 7 GND Ground 1 8 LVTTL-I ModSeil Module Select 3 9 LVTTL-I ResetL Module Reset 3 10 Vcc Rx +3.3 VDC Receiver Power Supply 2 11 LVCMOS-I/O SCL Serial Clock for I2C Interface 3 12 LVCMOS-I/O SDA Serial Data for I2C Interface 3 13 GND Ground 1 14 CML-O RX3p Receiver Non-Inverted Data Output 3 15 CML-O RX3n Receiver Inverted Data Output 3 16 GND Ground 1 17 CML-O RX1p Receiver Non-Inverted Data Output 3 18 CML-O RX1p Receiver Non-Inverted Data Output 3 19 GND Ground 1 20 GND Ground 1 21 CML-O RX2n Receiver Inverted Data Output 3 22 CML-O RX2n Receiver Inverted Data Output 3 23 GND Ground 1 24 CML-O RX2p Receiver Inverted Data Output 3 25 CML-O RX4p Receiver Inverted Data Output 3 26 GND Ground 1 27 LVTTL-O ModPrsL Receiver Inverted Data Output 3 28 LVTTL-O IntL Interrupt 3 29 Vcc Tx +3.3 VDC Transmitter Power Supply 2 30 Vcc1 +3.3 VDC Power Supply 2 31 LVTTL-I LPMode Low Power Mode 3 32 GND Ground 1 33 CML-I TX3p Transmitted Non-Inverted Data Input 3 34 CML-I TX1p Transmitted Inverted Data Input 3 35 GNL-I TX1p Transmitted Inverted Data Input 3 37 CML-I TX1p Transmitted Inverted Data Input 3 37 CML-I TX1n Transmitted Inverted Data Input 3                                            |          |            |         | <u> </u>                            |               |

| 5 CML-I TX4n Transmitted Inverted Data Input 3 6 CML-I TX4p Transmitted Non-Inverted Data Input 3 7 GND Ground 1 8 LYTTL-I ModSeil Module Select 3 9 LVTTL-I ResetL Module Reset 3 10 Vcc Rx +3.3 VDC Receiver Power Supply 2 11 LVCMOS-I/O SCL Serial Clock for I2C Interface 3 12 LVCMOS-I/O SDA Serial Data for I2C Interface 3 13 GND Ground 1 14 CML-O RX3p Receiver Non-Inverted Data Output 3 15 CML-O RX3n Receiver Inverted Data Output 3 16 GND Ground 1 17 CML-O RX1p Receiver Non-Inverted Data Output 3 18 CML-O RX1p Receiver Inverted Data Output 3 19 GND Ground 1 20 GND Ground 1 21 CML-O RX2n Receiver Inverted Data Output 3 22 CML-O RX2n Receiver Inverted Data Output 3 23 GND Ground 1 24 CML-O RX4n Receiver Inverted Data Output 3 25 CML-O RX4p Receiver Inverted Data Output 3 26 GND Ground 1 27 LVTTL-O ModPrsL Module Present 3 28 LVTTL-O IntL Interrupt 3 29 Vcc Tx +3.3 VDC Power Supply 2 30 Vcc Tx +3.3 VDC Power Supply 2 31 LVTTL-I LPMode Low Power Mode 3 32 GND Ground 1 33 CML-I TX3p Transmitted Non-Inverted Data Input 3 34 CML-I TX3p Transmitted Inverted Data Input 3 35 GND Ground 1 36 CML-I TX1p Transmitted Non-Inverted Data Input 3 37 CML-I TX1p Transmitted Inverted Data Input 3 37 CML-I TX1n Transmitted Inverted Data Input 3                                                                |          | CIVIE      | -       | ·                                   | _             |

| 6 CML-I TX4p Transmitted Non-Inverted Data Input 3 7 GND Ground 1 8 LVTTL-I ModSeil Module Select 3 9 LVTTL-I Resett Module Reset 3 10 Vcc Rx +3.3 VDC Receiver Power Supply 2 11 LVCMOS-I/O SCL Serial Clock for IZC Interface 3 12 LVCMOS-I/O SDA Serial Data for IZC Interface 3 13 GND Ground 1 14 CML-O RX3p Receiver Non-Inverted Data Output 3 15 CML-O RX3n Receiver Inverted Data Output 3 16 GND Ground 1 17 CML-O RX1p Receiver Non-Inverted Data Output 3 18 CML-O RX1p Receiver Inverted Data Output 3 19 GND Ground 1 20 GND Ground 1 21 CML-O RX2n Receiver Inverted Data Output 3 22 CML-O RX2n Receiver Inverted Data Output 3 23 GND Ground 1 24 CML-O RX2p Receiver Non-Inverted Data Output 3 25 CML-O RX4p Receiver Inverted Data Output 3 26 GND Ground 1 27 LVTTL-O RX4p Receiver Inverted Data Output 3 28 LVTL-O RX4p Receiver Non-Inverted Data Output 3 29 GND Ground 1 20 GND Ground 1 21 CML-O RX4p Receiver Inverted Data Output 3 25 CML-O RX4p Receiver Inverted Data Output 3 26 GND Ground 1 27 LVTTL-O ModPrsL Module Present 3 28 LVTTL-O IntL Interrupt 3 29 Vcc TX +3.3 VDC Transmitter Power Supply 2 30 Vcc1 +3.3 VDC Power Supply 2 31 LVTTL-I LPMode Low Power Mode 3 32 GND Ground 1 33 CML-I TX3p Transmitted Inverted Data Input 3 34 CML-I TX3p Transmitted Inverted Data Input 3 35 GND Ground 1          |          | CMI-I      |         |                                     |               |

| 7         GND         Ground         1           8         LVTTL-I         ModSeil         Module Select         3           9         LVTTL-I         ResetL         Module Reset         3           10         Vcc Rx         +3.3 VDC Receiver Power Supply         2           11         LVCMOS-I/O         SCL         Serial Clock for I2C Interface         3           12         LVCMOS-I/O         SDA         Serial Data for I2C Interface         3           13         GND         Ground         1           14         CML-O         RX3p         Receiver Non-Inverted Data Output         3           15         CML-O         RX3n         Receiver Inverted Data Output         3           16         GND         Ground         1           17         CML-O         RX1p         Receiver Inverted Data Output         3           18         CML-O         RX1n         Receiver Inverted Data Output         3           19         GND         Ground         1         1           20         GND         Ground         1         1           21         CML-O         RX2p         Receiver Non-Inverted Data Output         3         3                                                                                                                                                                                 | <u> </u> | CIVIE      | IATII   | Transmitted inverted bata input     | 3             |

| 8         LVTTL-I         ModSeil         Module Select         3           9         LVTTL-I         ResetL         Module Reset         3           10         Vcc Rx         +3.3 VDC Receiver Power Supply         2           11         LVCMOS-I/O         SCL         Serial Clock for I2C Interface         3           12         LVCMOS-I/O         SDA         Serial Data for I2C Interface         3           13         GND         Ground         1           14         CML-O         RX3p         Receiver Non-Inverted Data Output         3           15         CML-O         RX3n         Receiver Inverted Data Output         3           16         GND         Ground         1           17         CML-O         RX1n         Receiver Inverted Data Output         3           18         CML-O         RX1n         Receiver Inverted Data Output         3           20         GND         Ground         1         1           21         CML-O         RX2p         Receiver Inverted Data Output         3           22         CML-O         RX4n         Receiver Inverted Data Output         3           23         GND         Ground         1 </td <td>6</td> <td>CML-I</td> <td>TX4p</td> <td>Transmitted Non-Inverted Data Input</td> <td>3</td>                                                             | 6        | CML-I      | TX4p    | Transmitted Non-Inverted Data Input | 3             |

| 9         LVTTL-I         ResetL         Module Reset         3           10         VCC RX         +3.3 VDC Receiver Power Supply         2           11         LVCMOS-I/O         SCL         Serial Clock for I2C Interface         3           12         LVCMOS-I/O         SDA         Serial Data for I2C Interface         3           13         GND         Ground         1           14         CML-O         RX3p         Receiver Non-Inverted Data Output         3           15         CML-O         RX3n         Receiver Inverted Data Output         3           16         GND         Ground         1           17         CML-O         RX1p         Receiver Non-Inverted Data Output         3           18         CML-O         RX1n         Receiver Inverted Data Output         3           19         GND         Ground         1         1           20         GND         Ground         1         1           21         CML-O         RX2p         Receiver Inverted Data Output         3           22         CML-O         RX4p         Receiver Inverted Data Output         3           23         GND         Ground         1                                                                                                                                                                              | 7        |            | GND     | Ground                              | 1             |

| 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 8        | LVTTL-I    | ModSeil | Module Select                       | 3             |

| 11         LVCMOS-I/O         SCL         Serial Clock for I2C Interface         3           12         LVCMOS-I/O         SDA         Serial Data for I2C Interface         3           13         GND         Ground         1           14         CML-O         RX3p         Receiver Non-Inverted Data Output         3           15         CML-O         RX1p         Receiver Inverted Data Output         3           16         GND         Ground         1           17         CML-O         RX1p         Receiver Non-Inverted Data Output         3           18         CML-O         RX1n         Receiver Inverted Data Output         3           19         GND         Ground         1           20         GND         Ground         1           21         CML-O         RX2n         Receiver Inverted Data Output         3           22         CML-O         RX2p         Receiver Non-Inverted Data Output         3           23         GND         Ground         1           24         CML-O         RX4p         Receiver Non-Inverted Data Output         3           25         CML-O         RX4p         Receiver Non-Inverted Data Output         3                                                                                                                                                             | 9        | LVTTL-I    | ResetL  | Module Reset                        | 3             |

| 12         LVCMOS-I/O         SDA         Serial Data for I2C Interface         3           13         GND         Ground         1           14         CML-O         RX3p         Receiver Non-Inverted Data Output         3           15         CML-O         RX3n         Receiver Inverted Data Output         3           16         GND         Ground         1           17         CML-O         RX1p         Receiver Non-Inverted Data Output         3           18         CML-O         RX1n         Receiver Inverted Data Output         3           19         GND         Ground         1           20         GND         Ground         1           21         CML-O         RX2n         Receiver Inverted Data Output         3           22         CML-O         RX4p         Receiver Non-Inverted Data Output         3           23         GND         Ground         1           24         CML-O         RX4p         Receiver Non-Inverted Data Output         3           25         CML-O         RX4p         Receiver Non-Inverted Data Output         3           26         GND         Ground         1           27         LVTIL-O <td>10</td> <td></td> <td>Vcc Rx</td> <td>+3.3 VDC Receiver Power Supply</td> <td>2</td>                                                                                  | 10       |            | Vcc Rx  | +3.3 VDC Receiver Power Supply      | 2             |

| 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 11       | LVCMOS-I/O | SCL     | Serial Clock for I2C Interface      | 3             |

| 14 CML-O RX3p Receiver Non-Inverted Data Output 3 15 CML-O RX3n Receiver Inverted Data Output 3 16 GND Ground 1 17 CML-O RX1p Receiver Non-Inverted Data Output 3 18 CML-O RX1n Receiver Inverted Data Output 3 19 GND Ground 1 20 GND Ground 1 21 CML-O RX2n Receiver Inverted Data Output 3 22 CML-O RX2n Receiver Inverted Data Output 3 23 GND Ground 1 24 CML-O RX4n Receiver Inverted Data Output 3 25 CML-O RX4n Receiver Inverted Data Output 3 26 GND Ground 1 27 LVTTL-O RX4p Receiver Non-Inverted Data Output 3 28 LVTTL-O IntL Interrupt 3 29 Vcc Tx +3.3 VDC Transmitter Power Supply 2 30 Vcc1 +3.3 VDC Power Supply 2 31 LVTTL-I LPMode Low Power Mode 3 32 GND Ground 1 33 CML-I TX3p Transmitted Inverted Data Input 3 36 CML-I TX1p Transmitted Non-Inverted Data Input 3 37 CML-I TX1p Transmitted Inverted Data Input 3 37 CML-I TX1p Transmitted Inverted Data Input 3 37 CML-I TX1n Transmitted Inverted Data Input 3                                                                                                                                                                                                                                                                                                                                                                                                             | 12       | LVCMOS-I/O | SDA     | Serial Data for I2C Interface       | 3             |

| 15 CML-O RX3n Receiver Inverted Data Output 3 16 GND Ground 1 17 CML-O RX1p Receiver Non-Inverted Data Output 3 18 CML-O RX1n Receiver Inverted Data Output 3 19 GND Ground 1 20 GND Ground 1 21 CML-O RX2n Receiver Inverted Data Output 3 22 CML-O RX2n Receiver Inverted Data Output 3 23 GND Ground 1 24 CML-O RX4p Receiver Non-Inverted Data Output 3 25 CML-O RX4p Receiver Inverted Data Output 3 26 GND Ground 1 27 LVTTL-O ModPrsL Module Present 3 28 LVTTL-O IntL Interrupt 3 29 Vcc Tx +3.3 VDC Transmitter Power Supply 2 30 Vcc1 +3.3 VDC Power Supply 2 31 LVTTL-I LPMode Low Power Mode 3 32 GND Ground 1 33 CML-I TX3p Transmitted Inverted Data Input 3 34 CML-I TX3n Transmitted Inverted Data Input 3 36 CML-I TX1p Transmitted Inverted Data Input 3 37 CML-I TX1n Transmitted Inverted Data Input 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 13       |            | GND     | Ground                              | 1             |

| 15 CML-O RX3n Receiver Inverted Data Output 3 16 GND Ground 1 17 CML-O RX1p Receiver Non-Inverted Data Output 3 18 CML-O RX1n Receiver Inverted Data Output 3 19 GND Ground 1 20 GND Ground 1 21 CML-O RX2n Receiver Inverted Data Output 3 22 CML-O RX2n Receiver Inverted Data Output 3 23 GND Ground 1 24 CML-O RX4p Receiver Non-Inverted Data Output 3 25 CML-O RX4p Receiver Inverted Data Output 3 26 GND Ground 1 27 LVTTL-O ModPrsL Module Present 3 28 LVTTL-O IntL Interrupt 3 29 Vcc Tx +3.3 VDC Transmitter Power Supply 2 30 Vcc1 +3.3 VDC Power Supply 2 31 LVTTL-I LPMode Low Power Mode 3 32 GND Ground 1 33 CML-I TX3p Transmitted Inverted Data Input 3 34 CML-I TX3n Transmitted Inverted Data Input 3 36 CML-I TX1p Transmitted Inverted Data Input 3 37 CML-I TX1n Transmitted Inverted Data Input 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |            |         |                                     |               |

| 15 CML-O RX3n Receiver Inverted Data Output 3 16 GND Ground 1 17 CML-O RX1p Receiver Non-Inverted Data Output 3 18 CML-O RX1n Receiver Inverted Data Output 3 19 GND Ground 1 20 GND Ground 1 21 CML-O RX2n Receiver Inverted Data Output 3 22 CML-O RX2n Receiver Inverted Data Output 3 23 GND Ground 1 24 CML-O RX4p Receiver Non-Inverted Data Output 3 25 CML-O RX4p Receiver Inverted Data Output 3 26 GND Ground 1 27 LVTTL-O ModPrsL Module Present 3 28 LVTTL-O IntL Interrupt 3 29 Vcc Tx +3.3 VDC Transmitter Power Supply 2 30 Vcc1 +3.3 VDC Power Supply 2 31 LVTTL-I LPMode Low Power Mode 3 32 GND Ground 1 33 CML-I TX3p Transmitted Inverted Data Input 3 34 CML-I TX3n Transmitted Inverted Data Input 3 36 CML-I TX1p Transmitted Inverted Data Input 3 37 CML-I TX1n Transmitted Inverted Data Input 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 14       | CML-O      | RX3p    | Receiver Non-Inverted Data Output   | 3             |

| 16 GND Ground 1 17 CML-O RX1p Receiver Non-Inverted Data Output 3 18 CML-O RX1n Receiver Inverted Data Output 3 19 GND Ground 1 20 GND Ground 1 21 CML-O RX2n Receiver Inverted Data Output 3 22 CML-O RX2n Receiver Inverted Data Output 3 23 GND Ground 1 24 CML-O RX4n Receiver Inverted Data Output 3 25 CML-O RX4p Receiver Inverted Data Output 3 26 GND Ground 1 27 LVTTL-O ModPrsL Module Present 3 28 LVTTL-O IntL Interrupt 3 29 Vcc Tx +3.3 VDC Transmitter Power Supply 2 30 Vcc1 +3.3 VDC Power Supply 2 31 LVTTL-I LPMode Low Power Mode 3 32 GND Ground 1 33 CML-I TX3p Transmitted Non-Inverted Data Input 3 34 CML-I TX3n Transmitted Inverted Data Input 3 35 GND Ground 1 37 CML-I TX1p Transmitted Inverted Data Input 3 37 CML-I TX1n Transmitted Inverted Data Input 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 15       | CML-O      | -       |                                     |               |

| 17 CML-O RX1p Receiver Non-Inverted Data Output 3 18 CML-O RX1n Receiver Inverted Data Output 3 19 GND Ground 1 20 GND Ground 1 21 CML-O RX2n Receiver Inverted Data Output 3 22 CML-O RX2p Receiver Inverted Data Output 3 23 GND Ground 1 24 CML-O RX4n Receiver Inverted Data Output 3 25 CML-O RX4p Receiver Inverted Data Output 3 26 GND Ground 1 27 LVTTL-O ModPrsL Module Present 3 28 LVTTL-O IntL Interrupt 3 29 Vcc Tx +3.3 VDC Transmitter Power Supply 2 30 Vcc1 +3.3 VDC Power Supply 2 31 LVTTL-I LPMode Low Power Mode 3 32 GND Ground 1 33 CML-I TX3p Transmitted Inverted Data Input 3 34 CML-I TX3n Transmitted Inverted Data Input 3 35 GND Ground 1 36 CML-I TX1p Transmitted Non-Inverted Data Input 3 37 CML-I TX1n Transmitted Inverted Data Input 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |            |         | ·                                   |               |

| 18 CML-O RX1n Receiver Inverted Data Output 3 19 GND Ground 1 20 GND Ground 1 21 CML-O RX2n Receiver Inverted Data Output 3 22 CML-O RX2p Receiver Non-Inverted Data Output 3 23 GND Ground 1 24 CML-O RX4n Receiver Inverted Data Output 3 25 CML-O RX4p Receiver Inverted Data Output 3 26 GND Ground 1 27 LVTTL-O ModPrsL Module Present 3 28 LVTTL-O IntL Interrupt 3 29 Vcc Tx +3.3 VDC Transmitter Power Supply 2 30 Vcc1 +3.3 VDC Power Supply 2 31 LVTTL-I LPMode Low Power Mode 3 32 GND Ground 1 33 CML-I TX3p Transmitted Non-Inverted Data Input 3 34 CML-I TX3n Transmitted Inverted Data Input 3 35 GND Ground 1 36 CML-I TX1p Transmitted Non-Inverted Data Input 3 37 CML-I TX1n Transmitted Inverted Data Input 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          | CMI-O      |         |                                     | _             |

| 19         GND         Ground         1           20         GND         Ground         1           21         CML-O         RX2n         Receiver Inverted Data Output         3           22         CML-O         RX2p         Receiver Non-Inverted Data Output         3           23         GND         Ground         1           24         CML-O         RX4n         Receiver Inverted Data Output         3           25         CML-O         RX4p         Receiver Non-Inverted Data Output         3           26         GND         Ground         1           27         LVTTL-O         ModPrsL         Module Present         3           28         LVTTL-O         IntL         Interrupt         3           29         Vcc Tx         +3.3 VDC Transmitter Power Supply         2           30         Vcc1         +3.3 VDC Power Supply         2           31         LVTTL-I         LPMode         Low Power Mode         3           32         GND         Ground         1           33         CML-I         TX3p         Transmitted Inverted Data Input         3           34         CML-I         TX1p         Transmitted Non-Inve                                                                                                                                                                                |          |            | -       | ·                                   | _             |

| GND Ground 1  21 CML-O RX2n Receiver Inverted Data Output 3  22 CML-O RX2p Receiver Non-Inverted Data Output 3  23 GND Ground 1  24 CML-O RX4n Receiver Inverted Data Output 3  25 CML-O RX4p Receiver Non-Inverted Data Output 3  26 GND Ground 1  27 LVTTL-O ModPrsL Module Present 3  28 LVTTL-O IntL Interrupt 3  29 Vcc Tx +3.3 VDC Transmitter Power Supply 2  30 Vcc1 +3.3 VDC Power Supply 2  31 LVTTL-I LPMode Low Power Mode 3  32 GND Ground 1  33 CML-I TX3p Transmitted Non-Inverted Data Input 3  34 CML-I TX3n Transmitted Inverted Data Input 3  35 GND Ground 1  36 CML-I TX1p Transmitted Non-Inverted Data Input 3  37 CML-I TX1n Transmitted Inverted Data Input 3  37 CML-I TX1n Transmitted Inverted Data Input 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          | CIVIL      |         | ·                                   | -             |

| 22 CML-O RX2p Receiver Inverted Data Output 3 23 GND Ground 1 24 CML-O RX4n Receiver Inverted Data Output 3 25 CML-O RX4p Receiver Non-Inverted Data Output 3 26 GND Ground 1 27 LVTTL-O ModPrsL Module Present 3 28 LVTTL-O IntL Interrupt 3 29 Vcc Tx +3.3 VDC Transmitter Power Supply 2 30 Vcc1 +3.3 VDC Power Supply 2 31 LVTTL-I LPMode Low Power Mode 3 32 GND Ground 1 33 CML-I TX3p Transmitted Non-Inverted Data Input 3 34 CML-I TX3n Transmitted Inverted Data Input 3 35 GND Ground 1 36 CML-I TX1p Transmitted Non-Inverted Data Input 3 37 CML-I TX1n Transmitted Inverted Data Input 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |            |         |                                     | _             |

| 22 CML-O RX2p Receiver Non-Inverted Data Output 3 23 GND Ground 1 24 CML-O RX4n Receiver Inverted Data Output 3 25 CML-O RX4p Receiver Non-Inverted Data Output 3 26 GND Ground 1 27 LVTTL-O ModPrsL Module Present 3 28 LVTTL-O IntL Interrupt 3 29 Vcc Tx +3.3 VDC Transmitter Power Supply 2 30 Vcc1 +3.3 VDC Power Supply 2 31 LVTTL-I LPMode Low Power Mode 3 32 GND Ground 1 33 CML-I TX3p Transmitted Non-Inverted Data Input 3 34 CML-I TX3n Transmitted Inverted Data Input 3 35 GND Ground 1 36 CML-I TX1p Transmitted Non-Inverted Data Input 3 37 CML-I TX1n Transmitted Inverted Data Input 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          | CMI-O      |         |                                     |               |

| 23         GND         Ground         1           24         CML-O         RX4n         Receiver Inverted Data Output         3           25         CML-O         RX4p         Receiver Non-Inverted Data Output         3           26         GND         Ground         1           27         LVTTL-O         ModPrsL         Module Present         3           28         LVTTL-O         IntL         Interrupt         3           29         Vcc Tx         +3.3 VDC Transmitter Power Supply         2           30         Vcc1         +3.3 VDC Power Supply         2           31         LVTTL-I         LPMode         Low Power Mode         3           32         GND         Ground         1           33         CML-I         TX3p         Transmitted Non-Inverted Data Input         3           34         CML-I         TX3n         Transmitted Inverted Data Input         3           36         CML-I         TX1p         Transmitted Non-Inverted Data Input         3           37         CML-I         TX1n         Transmitted Inverted Data Input         3                                                                                                                                                                                                                                                       | 21       | CIVIL O    | IVAZII  | neceiver inverted bata output       | 3             |

| 24 CML-O RX4n Receiver Inverted Data Output 3 25 CML-O RX4p Receiver Non-Inverted Data Output 3 26 GND Ground 1 27 LVTTL-O ModPrsL Module Present 3 28 LVTTL-O IntL Interrupt 3 29 Vcc Tx +3.3 VDC Transmitter Power Supply 2 30 Vcc1 +3.3 VDC Power Supply 2 31 LVTTL-I LPMode Low Power Mode 3 32 GND Ground 1 33 CML-I TX3p Transmitted Non-Inverted Data Input 3 34 CML-I TX3n Transmitted Inverted Data Input 3 35 GND Ground 1 36 CML-I TX1p Transmitted Non-Inverted Data Input 3 37 CML-I TX1n Transmitted Inverted Data Input 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 22       | CML-O      | RX2p    | Receiver Non-Inverted Data Output   | 3             |

| 25 CML-O RX4p Receiver Non-Inverted Data Output 3 26 GND Ground 1 27 LVTTL-O ModPrsL Module Present 3 28 LVTTL-O IntL Interrupt 3 29 Vcc Tx +3.3 VDC Transmitter Power Supply 2 30 Vcc1 +3.3 VDC Power Supply 2 31 LVTTL-I LPMode Low Power Mode 3 32 GND Ground 1 33 CML-I TX3p Transmitted Non-Inverted Data Input 3 34 CML-I TX3n Transmitted Inverted Data Input 3 35 GND Ground 1 36 CML-I TX1p Transmitted Non-Inverted Data Input 3 37 CML-I TX1p Transmitted Non-Inverted Data Input 3 38 CML-I TX1p Transmitted Non-Inverted Data Input 3 39 CML-I TX1p Transmitted Inverted Data Input 3 31 CML-I TX1p Transmitted Inverted Data Input 3 32 CML-I TX1p Transmitted Inverted Data Input 3 39 CML-I TX1p Transmitted Inverted Data Input 3 30 CML-I TX1n Transmitted Inverted Data Input 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 23       |            | GND     | Ground                              | 1             |

| 25 CML-O RX4p Receiver Non-Inverted Data Output 3 26 GND Ground 1 27 LVTTL-O ModPrsL Module Present 3 28 LVTTL-O IntL Interrupt 3 29 Vcc Tx +3.3 VDC Transmitter Power Supply 2 30 Vcc1 +3.3 VDC Power Supply 2 31 LVTTL-I LPMode Low Power Mode 3 32 GND Ground 1 33 CML-I TX3p Transmitted Non-Inverted Data Input 3 34 CML-I TX3n Transmitted Inverted Data Input 3 35 GND Ground 1 36 CML-I TX1p Transmitted Non-Inverted Data Input 3 37 CML-I TX1p Transmitted Non-Inverted Data Input 3 38 CML-I TX1p Transmitted Non-Inverted Data Input 3 39 CML-I TX1p Transmitted Inverted Data Input 3 31 CML-I TX1p Transmitted Inverted Data Input 3 32 CML-I TX1p Transmitted Inverted Data Input 3 39 CML-I TX1p Transmitted Inverted Data Input 3 30 CML-I TX1n Transmitted Inverted Data Input 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 24       | CML-O      | RX4n    | Receiver Inverted Data Output       | 3             |

| 26 GND Ground 1 27 LVTTL-O ModPrsL Module Present 3 28 LVTTL-O IntL Interrupt 3 29 Vcc Tx +3.3 VDC Transmitter Power Supply 2 30 Vcc1 +3.3 VDC Power Supply 2 31 LVTTL-I LPMode Low Power Mode 3 32 GND Ground 1 33 CML-I TX3p Transmitted Non-Inverted Data Input 3 34 CML-I TX3n Transmitted Inverted Data Input 3 35 GND Ground 1 36 CML-I TX1p Transmitted Non-Inverted Data Input 3 37 CML-I TX1n Transmitted Inverted Data Input 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 25       | CML-O      | RX4p    |                                     | 3             |

| 28 LVTTL-O IntL Interrupt 3 29 Vcc Tx +3.3 VDC Transmitter Power Supply 2 30 Vcc1 +3.3 VDC Power Supply 2 31 LVTTL-I LPMode Low Power Mode 3 32 GND Ground 1 33 CML-I TX3p Transmitted Non-Inverted Data Input 3 34 CML-I TX3n Transmitted Inverted Data Input 3 35 GND Ground 1 36 CML-I TX1p Transmitted Non-Inverted Data Input 3 37 CML-I TX1p Transmitted Non-Inverted Data Input 3 38 CML-I TX1p Transmitted Inverted Data Input 3 39 CML-I TX1p Transmitted Inverted Data Input 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 26       |            |         | ·                                   | 1             |

| 28 LVTTL-O IntL Interrupt 3 29 Vcc Tx +3.3 VDC Transmitter Power Supply 2 30 Vcc1 +3.3 VDC Power Supply 2 31 LVTTL-I LPMode Low Power Mode 3 32 GND Ground 1 33 CML-I TX3p Transmitted Non-Inverted Data Input 3 34 CML-I TX3n Transmitted Inverted Data Input 3 35 GND Ground 1 36 CML-I TX1p Transmitted Non-Inverted Data Input 3 37 CML-I TX1p Transmitted Non-Inverted Data Input 3 38 CML-I TX1p Transmitted Inverted Data Input 3 39 CML-I TX1p Transmitted Inverted Data Input 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 27       | LVTTL-O    | ModPrsL | Module Present                      | 3             |

| 29Vcc Tx+3.3 VDC Transmitter Power Supply230Vcc1+3.3 VDC Power Supply231LVTTL-ILPModeLow Power Mode332GNDGround133CML-ITX3pTransmitted Non-Inverted Data Input334CML-ITX3nTransmitted Inverted Data Input335GNDGround136CML-ITX1pTransmitted Non-Inverted Data Input337CML-ITX1nTransmitted Inverted Data Input3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 28       |            | IntL    | Interrupt                           | 3             |

| 30 Vcc1 +3.3 VDC Power Supply 2 31 LVTTL-I LPMode Low Power Mode 3 32 GND Ground 1 33 CML-I TX3p Transmitted Non-Inverted Data Input 3 34 CML-I TX3n Transmitted Inverted Data Input 3 35 GND Ground 1  36 CML-I TX1p Transmitted Non-Inverted Data Input 3 37 CML-I TX1n Transmitted Inverted Data Input 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |            | Vcc Tx  |                                     |               |

| 31 LVTTL-I LPMode Low Power Mode 3 32 GND Ground 1 33 CML-I TX3p Transmitted Non-Inverted Data Input 3 34 CML-I TX3n Transmitted Inverted Data Input 3 35 GND Ground 1  36 CML-I TX1p Transmitted Non-Inverted Data Input 3 37 CML-I TX1n Transmitted Inverted Data Input 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |            |         |                                     |               |

| 32 GND Ground 1 33 CML-I TX3p Transmitted Non-Inverted Data Input 3 34 CML-I TX3n Transmitted Inverted Data Input 3 35 GND Ground 1  36 CML-I TX1p Transmitted Non-Inverted Data Input 3 37 CML-I TX1n Transmitted Inverted Data Input 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          | LVTTL-I    |         | • • •                               |               |

| 33 CML-I TX3p Transmitted Non-Inverted Data Input 3 34 CML-I TX3n Transmitted Inverted Data Input 3 35 GND Ground 1  36 CML-I TX1p Transmitted Non-Inverted Data Input 3 37 CML-I TX1n Transmitted Inverted Data Input 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |            |         |                                     |               |

| 34 CML-I TX3n Transmitted Inverted Data Input 3 35 GND Ground 1  36 CML-I TX1p Transmitted Non-Inverted Data Input 3 37 CML-I TX1n Transmitted Inverted Data Input 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          | CML-I      | +       |                                     |               |

| 35 GND Ground 1  36 CML-I TX1p Transmitted Non-Inverted Data Input 3  37 CML-I TX1n Transmitted Inverted Data Input 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |            |         | ·                                   | _             |

| 36 CML-I TX1p Transmitted Non-Inverted Data Input 3 37 CML-I TX1n Transmitted Inverted Data Input 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |            |         | •                                   |               |

| 37 CML-I TX1n Transmitted Inverted Data Input 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |            |         |                                     | _             |

| 37 CML-I TX1n Transmitted Inverted Data Input 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 36       | CML-I      | TX1p    | Transmitted Non-Inverted Data Input | 3             |

| ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |            | •       |                                     |               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          | 5.0.2      |         | ·                                   |               |

## **High Speed Electrical Specifications**

| Transmitter Parameter                              | Min                          | Typical      | Max  | Unit |

|----------------------------------------------------|------------------------------|--------------|------|------|

| Signaling rate per lane (range)                    | e (range) 25.78125 ± 100 ppm |              |      | GBd  |

| AC common-mode output voltage (RMS)                |                              |              | 17.5 | mV   |

| Differential output voltage                        |                              |              | 900  | mV   |

| Eye width                                          | 0.57                         |              |      | UI   |

| Eye height, differential                           | 228                          |              |      | mV   |

| Vertical eye closure                               |                              |              | 5.5  | dB   |

| Differential output return loss                    | Equation (83E–2)             |              |      | dB   |

| Common to differential mode conversion return loss | Equation (83E–3)             |              |      | dB   |

| Differential termination mismatch                  |                              |              | 10   | %    |

| Transition time (20% to 80%)                       | 12                           |              |      | ps   |

| DC common mode voltage                             | -350                         |              | 2850 | mV   |

| Receiver Parameter                                 | Min                          | Typical      | Max  | Unit |

| Signaling rate per lane (range)                    | 25.781                       | 25 ± 100 ppm |      | GBd  |

| AC common-mode output voltage (RMS)                |                              |              | 17.5 | mV   |

| Differential output voltage                        |                              |              | 900  | mV   |

| Eye width                                          | 0.57                         |              |      | UI   |

| Eye height, differential                           | 228                          |              |      | mV   |

| Vertical eye closure                               |                              |              | 5.5  | dB   |

| Differential output return loss                    | Equation (83E–2)             |              |      | dB   |

| Common to differential mode conversion return loss | Equation (83E-3)             |              |      | dB   |

| Differential termination mismatch                  |                              |              | 10   | %    |

| Transition time ( 20% to 80%)                      | 12                           |              |      | ps   |

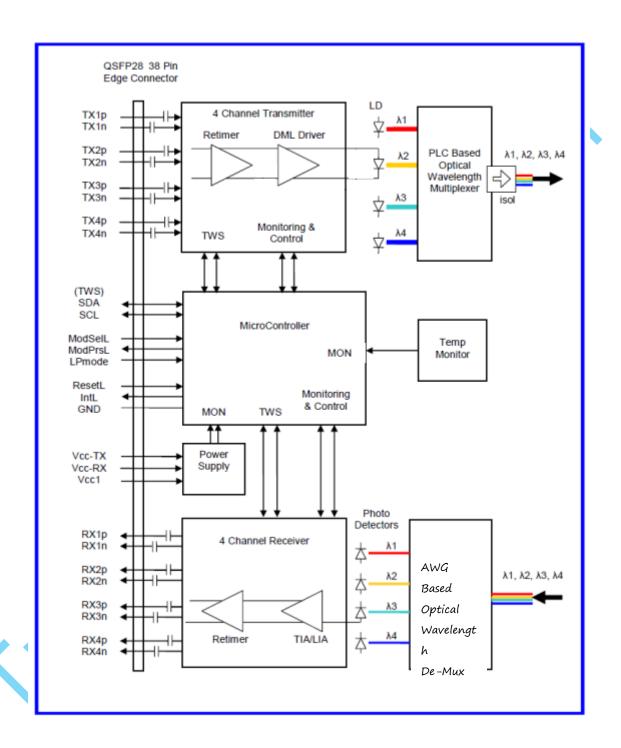

# **Functional Block Diagram**

Figure 2. Functional Block Diagram

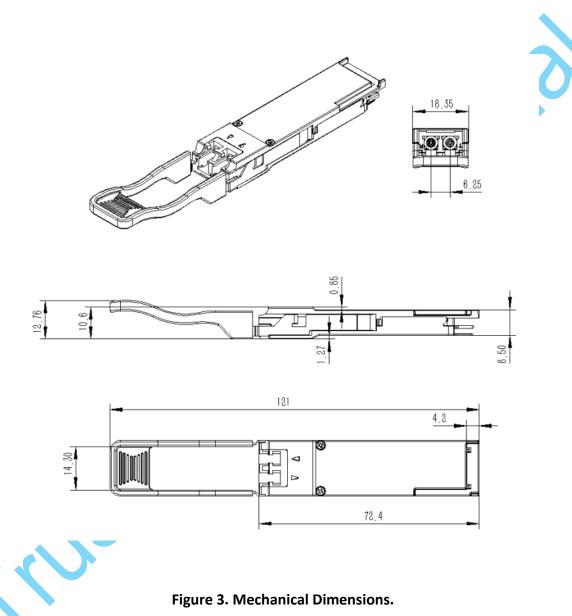

# **Mechanical Specifications**

Pull Tab Pantone: Blue

Pantone: 300U Unit: mm

# **Order information**

| Part Number     | Description                         |  |  |

|-----------------|-------------------------------------|--|--|

| TNQ2LW6XL-CD104 | QSFP28 100G LR4 Optical Transceiver |  |  |